Bei immer komplexeren Designs wird es mit herkömmlichen Methoden immer schwieriger, FPGAs effizient zu entwickeln und zuverlässig zu testen, um Fehler in einem frühen Stadium der Entwicklung zu finden.

Aus diesem Grunde ist es sinnvoll, die Entwicklung mittels einer Software vorzunehmen, die Sie in allen Stufen zuverlässig unterstützt und den Entwicklungsprozess effizienter gestaltet - bei gleichzeitig höherer Qualität!

Weiterbildung ist uns ein wichtiges Thema und so schulen wir unsere Kunden in innovativen Design- und Verifikationsprozessen sowie im Umgang mit unseren EDA- und ECAD-Lösungen.

Durch intensive und kompetente Beratung, maßgeschneiderte Lösungen und Weiterbildungen sorgen wir für die Digitalisierung in der Produktentwicklung - für kürzere Entwicklungszeiten, verbesserte Qualität und erhöhte Zuverlässigkeit.

So unterstützen wir Sie bei Ihrer Digitalen Transformation.

Workshop-Termine: Jetzt anmelden!

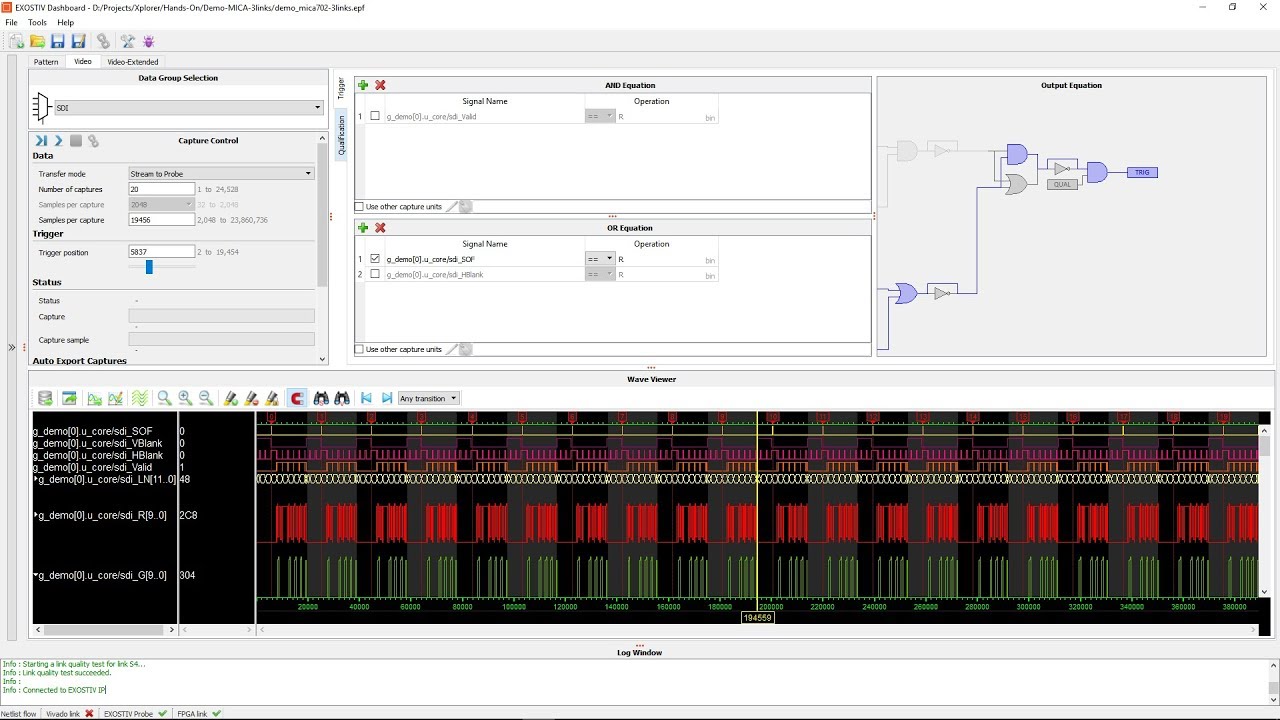

Klicken Sie auf das Bild, um mehr über den jeweiligen Kurs zu erfahren:

Der Kurs richtet sich an Verifikationsingenieure ohne UVM Vorwissen, die in die Nutzung von UVM Testbenches einsteigen wollen.

Ziel des Kurses ist es, eine vollständige UVM Testbench unter Verwendung des Siemens EDA UVM Frameworks (UVMF) zu erstellen, die dann an wenigen Stellen noch mit anwendungsspezifischem Code ergänzt wird.

Für Buchung oder einem Angebot vorab kontaktieren Sie uns unter +49 (0)2151/95301-0. Durch Klick auf den Button können Sie uns auch per E-Mail kontaktieren.