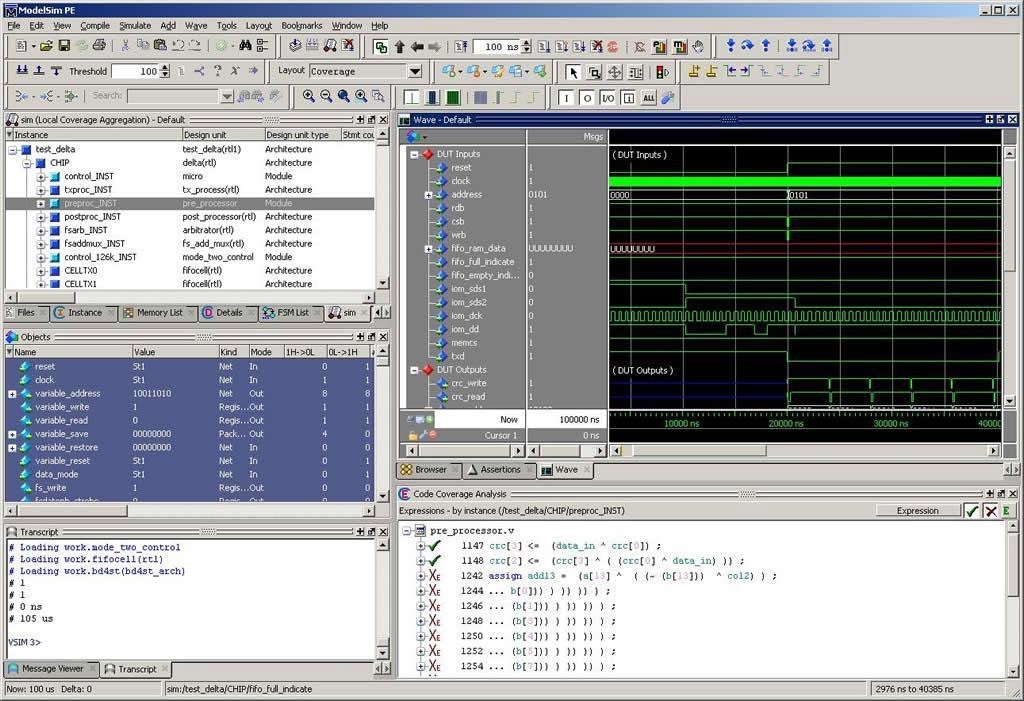

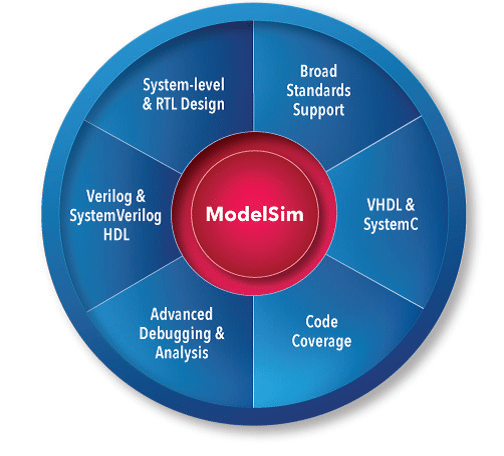

Was ist ModelSim?

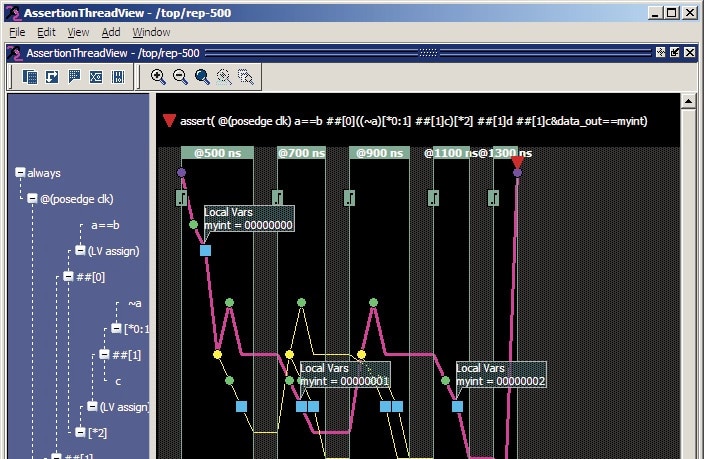

ModelSim ist eine mehrsprachige Simulationsumgebung von Siemens EDA, früher Mentor Graphics. Diese Simulationsumgebung für Hardwarebeschreibungssprachen (HDL) kommt mit einer intuitiven und leistungsstarken grafischen Oberfläche und ermöglicht eine taktsynchrone oder timinggenaue Simulation von Logikelementen.