- Sie befinden sich hier:

- Home »

- Unternehmen »

- Referenzkunden

Referenzkunden

ALAMO Engineering arbeitet seit Oktober 2019 täglich mit der Erstellung von elektrischen Konstruktionsdaten (Wiring Designs, BOME und Harness Manufacturing) mit Capital™ Essentials (ehemals VeSys®) Electrical Bundle, und mit dieser Erfahrung wächst die Leistungsfähigkeit in einer konkurrenzbetonten Industrie.

„Wir sehen die Vorteile von Capital™ Essentials (ehemals VeSys®) vor allem im Aufbau der Datenbank, bei schneller Implementierung, und Extraktion von verknüpften BOME, inklusive Generierung von Leitungs- und Stücklisten“, sagt Jörg Gorkenant, General Manager, ALAMO Engineering

Die Firma TRIAS betreut uns bei den Produkten „Siemens EDA Capital™ Essentials (ehemals VeSys®)“ und den dazugehörigen Schnittstellen zu „Siemens Teamcenter®“ und „Dassault Catia® V5“.

Die Beratung und Wartung rund um diese Produkte ist bei der Firma TRIAS sehr zufriedenstellend. Hervorzuheben ist die rasche Reaktion und fachliche Lösungskompetenz im Supportfall. Das ist für unser Projekte eine wesentliche Voraussetzung für eine reibungslose und termingetreue Abwicklung, welche wir unsererseits wieder an unsere Kunden weitergeben können.

Walter Nagel

IT Solution Architect

F. List GmbH

Nach einiger Recherche haben wir uns für Capital™ Essentials (ehemals VeSys®) Design und Capital™ Essentials (ehemals VeSys®) Harness als Werkzeuge für die Erstellung von Schaltplänen zur elektrischen Verdrahtung und Bildung von Kabelbäumen entschieden.

Durch die Einführung haben wir unsere Effizienz in der Erstellung erheblich gesteigert. Weiterhin konnten wir die Fehlerrate in der Erstellung deutlich reduzieren. Automatische Stücklisten, sowie eine Teilebibliothek, unterstützen uns bei der Erstellung. Weiterhin schätzen wir den exzellenten TRIAS Support, der schnell und kompetent zur Verfügung steht. Mit Vesys® haben wir ein Tool gefunden, was uns dabei hilft unsere eigenen Ziele schneller und einfacher zu erreichen und unseren Kunden das geforderte Ergebnis zu liefern.

Kai Odenthal

Deputy Head of Office of Airworthiness

CVE Avionics & Electrics

FTI Engineering Network GmbH

Die Zusammenarbeit mit der Fa. TRIAS mikroelektronik ist sehr vorbildlich, da wir ein vergleichsweise kleiner Kunde sind erhalten wir den gleichen zuvorkommenden Service wie alle anderen Firmen auch.

Die Kommunikation mit den Mitarbeitern und auch der Geschäftsführung ist immer freundlich und zuvorkommend.

Es wird nach pragmatischen, schnellen Lösungen gesucht und auch angeboten.

Einen besonderen Dank geht an die Marketingassistentin Frau Pacovsky und den CEO Herrn Steinheuer.

Rolf Latermann

CISO / ISMS u. DSB Beauftragter / Projektleiter

KSHG Auto Harness GmbH

Für unser Entwicklerteam haben wir sehr erfolgreich eine auf unsere Bedürfnisse zugeschnittene In-House Schulung durchgeführt. Diese war für Einsteiger und erfahrenen Ingenieuren gleichermaßen sehr gut umgesetzt. Zudem sind wir mit dem sehr schnellen und kompetenten Support von TRIAS sehr zufrieden.

Alexander Grünig

CTO

PCO AG

An der Zusammenarbeit mit der TRIAS Mikroelektronik schätzen wir insbesondere die gute Kundenbetreuung. Es werden schnell und unkompliziert Lösungen im angenehmen, persönlichen Dialog erarbeitet. Dies durften wir ganz besonders erfahren, als unser Unternehmen Opfer eines Cyberangriffs wurde. Hier unterstützte uns TRIAS Mikroelektronik umgehend und unbürokratisch, auch über vertraglich vereinbarte Leistungen hinaus.

Noch einmal vielen Dank dafür!

Winfried Gruber

Product Development

Pilz GmbH & Co KG

Capital™ Essentials (ehemals VeSys®) ist für mich das intuitivste und vielseitigste ECAD System für die Kabelbaumentwicklung. Kombiniert mit dem ausgezeichneten Support von TRIAS, gibt es in diesem Bereich keine Alternative, um hervorragende Entwicklungsarbeit zu leisten.

Als Part21-J Entwicklungs- und Musterprüfingenieur für Avionik ist die Erstellung und Prüfung von Schaltplänen Teil meines Aufgabenbereiches. Mit Capital™ Essentials (ehemals VeSys®) kann diese Aufgabe problemlos und zügig erledigt werden.

Markus Brunner

Inhaber

Pro Avionics

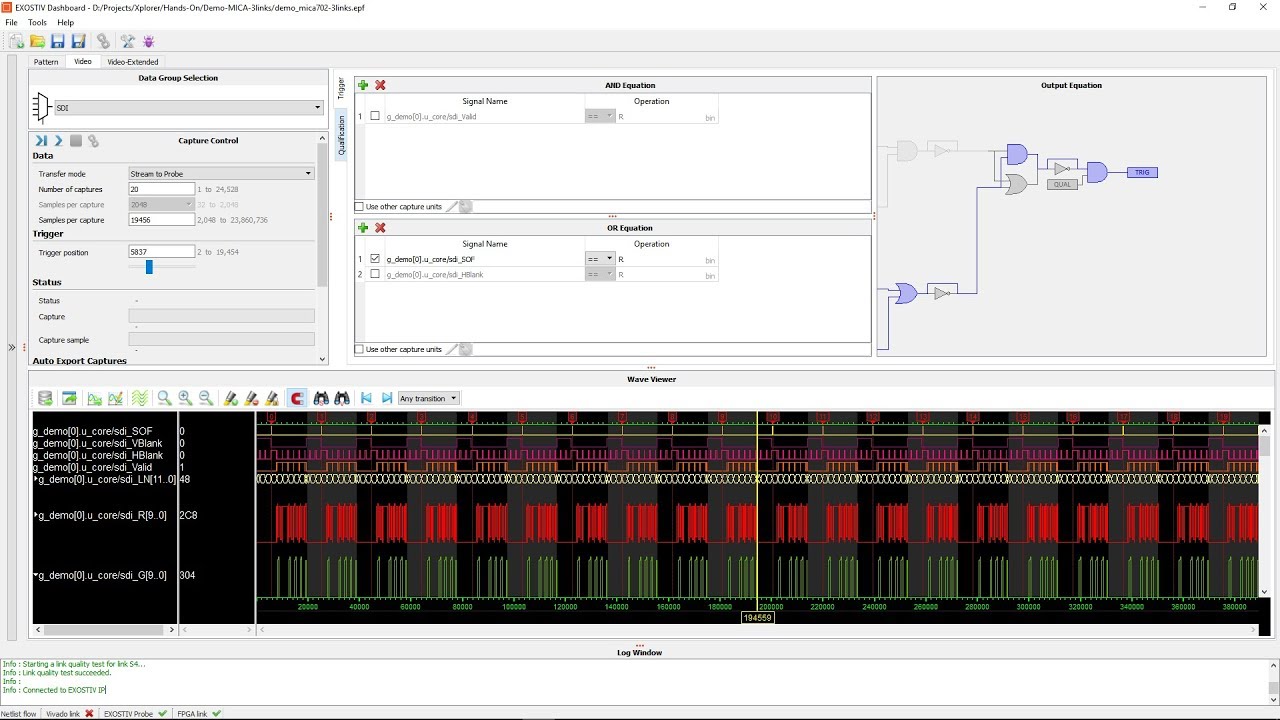

Ich beziehe seit vielen Jahren den ModelSim® HDL-Simulator von der TRIAS Mikroelektronik für unsere HDL- und System-Simulation und bin zufrieden mit dem Produkt und äußerst zufrieden mit der Betreuung der TRIAS Mikroelektronik. Es wurde auf unseren konkreten Bedarf detailliert eingegangen und unsere Situation aufmerksam berücksichtigt.

Zusätzlich schätze ich, dass die Inbetriebnahme und die Betriebsfähigkeit immer aktiv unterstützt wurde. Dies hält uns besonders zuverlässig arbeitsfähig. Ebenfalls schätze ich den fachlichen Austausch mit der TRIAS Mikroelektronik über das Geschäftliche hinaus. Es fand bisher ein regelmäßiger Austausch über relevante technische Neuerungen und unsere kundenspezifischen Bedürfnisse statt.

Dr. Markus Jäger

Inhaber

SciCaTec

Während der ersten Corona-Phase habe ich im Home-Office per Remoteverbindung auf meine Firmenrechner gearbeitet. Das ich nur eine Nodelocked-Lizenz habe, konnte ich ModelSim® auf diese Weise nicht nutzten. Damit ich auch im Home-Office mit ModelSim® arbeiten kann, hat TRIAS mir schnell und unkompliziert eine Floating-Lizenz zur Verfügung gestellt.

Eine gute Referenz, in schwierigen Zeiten einen verlässlichen Partner wie TRIAS zu haben.

Tobias Vollberg

Entwicklung

ZES ZIMMER Electronic Systems GmbH