Die Definition dessen, was FPGA wirklich bedeutet, hat sich in den letzten zwei Jahrzehnten dramatisch verändert. Es ist eine aufregende Zeit, um ein FPGA-Designer zu sein. Neue Möglichkeiten bringen neue Herausforderungen für den FPGA-Markt. Der moderne FPGA-Designer steht bei der Arbeit an seinem Projekt vor vielen verschiedenen Herausforderungen. Daher präsentieren wir Ihnen hier eine Reihe von Webinaren von Fachexperten zu den Themen FPGA Design und FPGA Verifikation.

FPGA VERIFICATION MADE MODERN

Webinar-Reihen

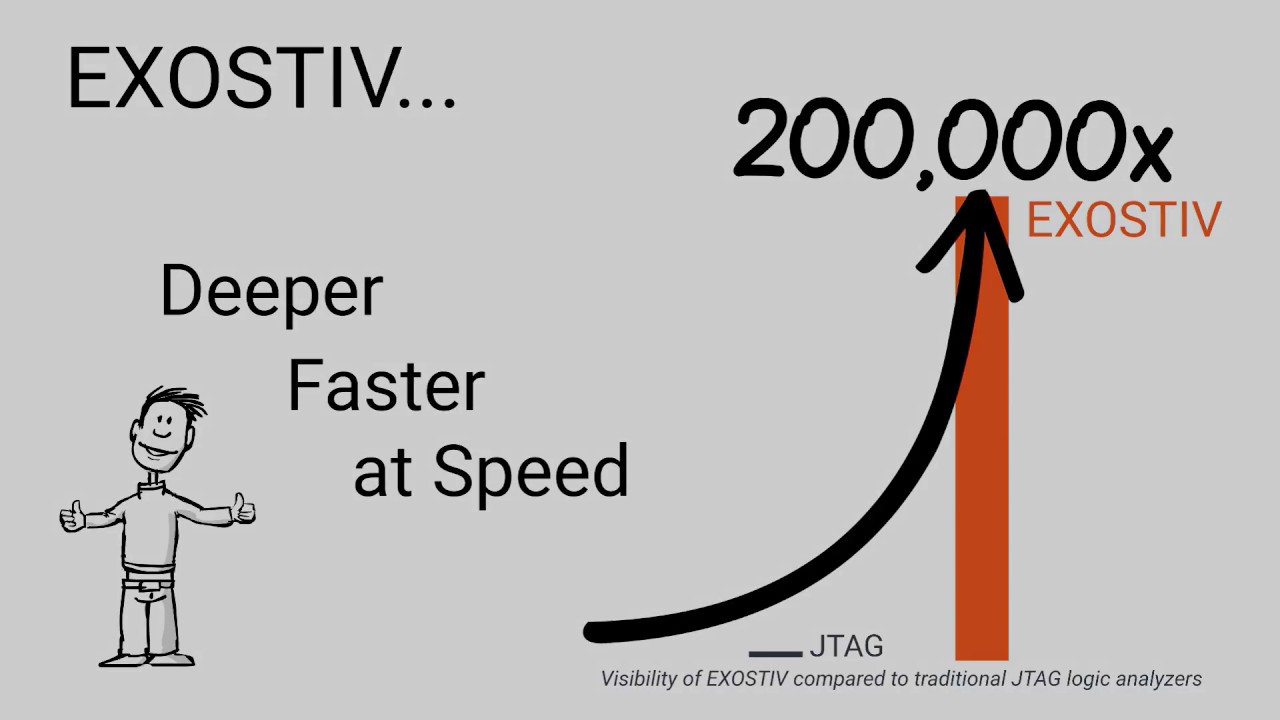

Die FPGA-Technologien entwickeln sich in der Komplexität rasant. Es werden immer mehr Funktionen implementiert und die Strukturen werden immer komplexer. Mehr Komplexität bedeutet mehr Zeitaufwand bei der Verifikation – bei traditionellen Simulationsansätzen.

Durch moderne Verifikationsmethoden und Tools kann dieser zeitintensive Aufwand reduziert werden, bei höherer Qualität und geringerer Fehlerquote bereits vor dem Prototyp!

Die jährlich stattfindenden technischen Webinar-Reihen „FPGA Verification Made Modern“ stellen unterschiedliche Verifikationsmethoden vor und berichten aus der Praxis. In den Webinaren stellen renommierte Experten aus dem FPGA-Bereich die Methoden und Lösungsansätze vor, die Ihnen beim FPGA Design und der Verifikation das Leben erleichtern.

Webinar-Reihe 2023

Anforderungsgetriebener HW-Entwurf und Verifizierung

Webinar-Reihe 2022

Webinar-Reihe 2021

Webinar-Reihe 2020

FPGA Verification Day 2023

ONLINE-KONFERENZ VORTRAGSREIHE

In seiner Keynote zeigt Dr. Michael Gude von Cologne Chip die architektonischen Neuerungen und Vorteile der GateMate FPGAs auf.

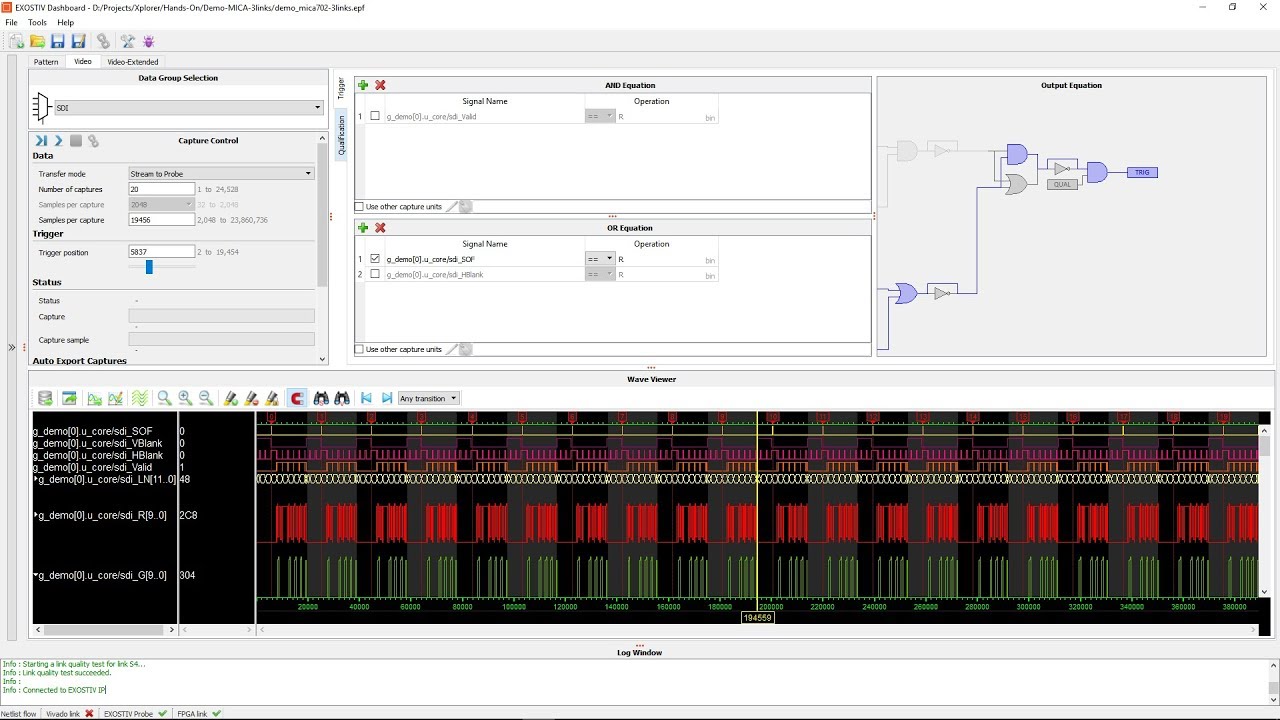

Hans-Jürgen Schwender von TRIAS mikroelektronik stellt die die Highlights der neuen Debug-Funktionen vor, die mit der Visualizer Debug UI verfügbar sind.

Wie man die Verification mit Questa Static Tools in CI Flows bei Teamprojekten optimieren kann, erklärt Faïçal Chtourou von Siemens EDA.

Espen Tallaksen von Emlogic bringt Ihnen näher, wie man die richtige FPGA Qualität durch effektive Specification Coverage erzielt.

In dem anschließenden Tutorial demonstriert er, wie man eine Testbench für eine korrekte Spezifikationsabdeckung erstellt.

Neil Rattray von Siemens EDA gibt Ihnen einen praktischen Leitfaden für den Einsatz der formalen Verifikation in Ihrer Designumgebung an die Hand.

Abschließend gibt Joachim Müller von Efinix ein Update über den High-Performance Quantum® FPGA in der Titanium Familie.