Beschreibung

Effizienz und Qualität sind eine Frage des Überblicks, der Lesbarkeit, der Erweiterbarkeit, der Wartbarkeit und der Wiederverwendung - und eine gute Testbench Architektur ist die Antwort. Dies gilt sowohl für das Design als auch für die Verifikation.

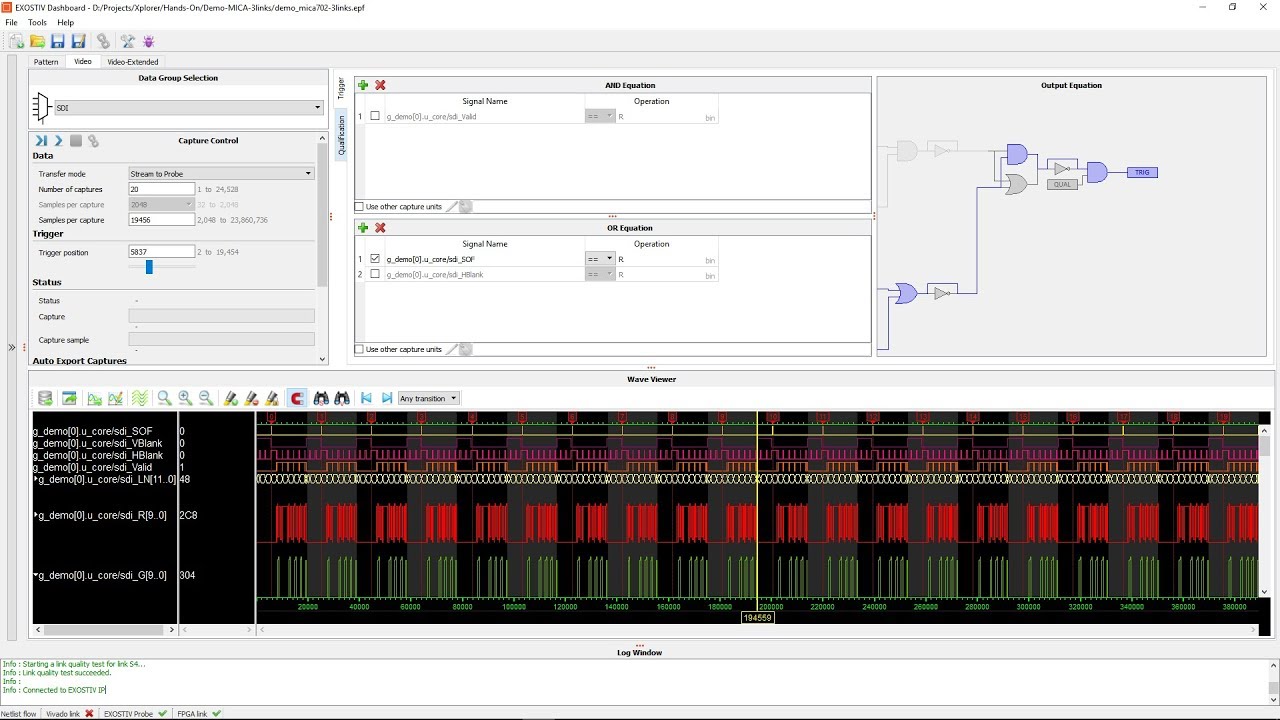

Dieser Kurs enthält eine allgemeine Einführung in die moderne Verifikationsmethode UVVM (Universal VHDL Verification Methodology) - die Nr. 1 der weltweit führenden VHDL-FPGA-Verifikationsmethoden, die unabhängig von HDL, den schnellsten Wachstum zeigt.

Im Durchschnitt entfällt fast die Hälfte der Zeit eines FPGA Projekts auf die Verifikation. Es ist möglich, diese Zeit erheblich zu verkürzen, und mit kleineren Anpassungen können sogar größere Einsparungen erreicht werden. In diesem Kurs lernen Sie, wie Sie die Entwicklungszeit verkürzen und gleichzeitig die Qualität verbessern können.

Kursziele

Nach dem Kurs wissen Teilnehmer, wie sie eine FPGA Verifikationsplattform strukturieren, ihre Testbenches implementieren und Testsequenzer schreiben können, damit sie auch von Software- und Hardware Entwicklern verstanden werden. Teilnehmer lernen außerdem die komplette, VHDL-basierte UVVM Verifikationsplattform in der eigenen Organisation anzuwenden.

der trainer

Espen Tallaksen

ist der CEO und Gründer von EmLogic, dem neugegründeten unabhängigen Designcenter für Embedded Software. Emlogic wird sicher, wie zuvor auch das von ihm gegründete Bitvis, ein führendes nordisches Unternehmen in seinem Bereich sein. Er absolvierte 1987 die Universität von Glasgow (Schottland) und verfügt über 30 Jahre Erfahrung in der FPGA- und ASIC-Entwicklung bei Philips Semiconductors in der Schweiz und verschiedenen Unternehmen in Norwegen. Seit zwanzig Jahren hat Espen ein besonderes Interesse an der Entwicklung von Methoden und der pragmatischen Effizienz- und Qualitätsverbesserung.

Ein Ergebnis dieses Interesses ist die UVVM-Verifizierungsplattform, die weltweit die Nummer 1 unter den VHDL-Verifizierungsmethoden und –Bibliotheken, und unabhängig von HDL, die am schnellsten wachsende FPGA-Verifizierungsmethode ist.

Er hat international zahlreiche Präsentationen und Keynotes zu verschiedenen technischen Aspekten der FPGA-Entwicklung gehalten, darunter seit 2016 jedes Jahr viele praktische Tutorials und Präsentationen auf dem FPGA-Kongress. - alle mit einem vollen Publikum und großartigem Feedback. Außerdem gibt er weltweit Kurse zum effizienteren und qualitativ besseren Entwerfen und Überprüfen von FPGAs.

Voraussetzungen: Kenntnisse der Sprache VHDL I Dauer: 5 Tage - 9:00 - 13:30 Uhr I Sprache: Englisch I Preis: 2.200,00 EUR netto