Design Erstellung

Egal, ob es sich um ein FPGA oder ASIC handelt, die Bausteine verfügen über erweiterte und komplexe Funktionen, die die Entwicklungsteams in enge Entwicklungszyklen zwingen, um effiziente und zuverlässige Chips zu produzieren. Daher stellen die Designteams mehr Anforderungen an HDL-Prozesse, Automatisierung und Code-Richtlinien für die Entwicklung von qualitativ hochwertigen Ergebnissen.

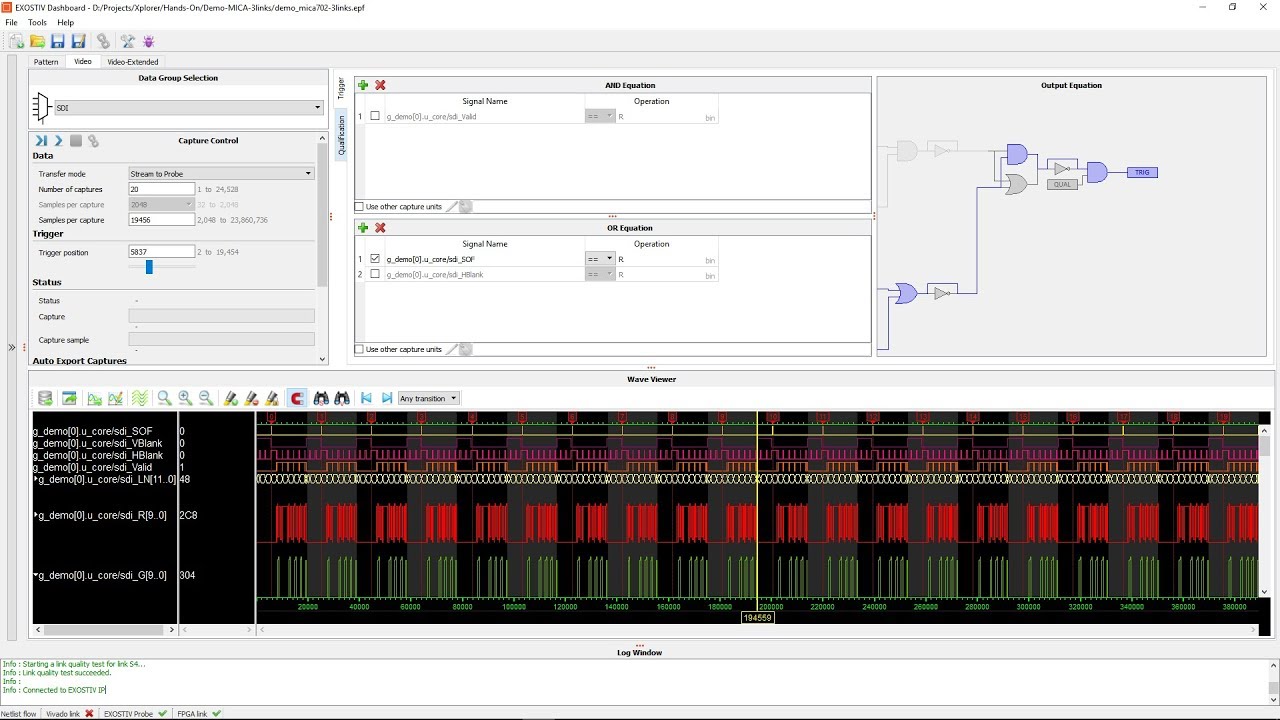

Standardsprachen (wie VHDL, Verilog, SystemVerilog) und IP-Formate unterstützen zusammen mit den gängigen Versionsverwaltungssystemen die Erstellung wiederholbarer und zuverlässiger Entwurfsprozesse. Aber die Tools, die diese Standards verwenden, müssen viel mehr können als nur Textdateien bearbeiten. Siemens EDA, früher Mentor Graphics, bietet eine vollständige Designlösung für FPGA- und ASIC-HDL-Entwicklung an, beginnend mit einer umfassenden Design-Erstellung, neuer Code-Erstellung, formale und informelle Designwiederverwendung und jede Kombination dazwischen. Diese HDL-Design-Funktionen unterstützen Ingenieure, als Einzelpersonen oder in Teams, bei der Erstellung, Analyse und Verwaltung ihrer komplexen Designs, verbessert ihre Produktivität und beschleunigt die Design-Erstellung.

DesignWiederverwendung

Effektive Designwiederverwendung ist ein entscheidendes Ziel für jedes Elektronikentwicklungsunternehmen. 75% der zukünftigen Produktivitätsgewinne werden durch Wiederverwendung erzielt. Führungskräfte, Manager und Ingenieure haben einen großen Anteil an der Wiederverwendung, aber fast jeder unterschätzt die damit verbundenen Herausforderungen.

Siemens EDA bietet Produkte der HDL Designer Series-Familie an, die innerhalb von Minuten die Designhierarchie automatisch erfassen, Syntaxfehler hervorheben und fehlende oder verwaiste Blöcke aufzeigen. Die Qualität des HDL-Codes wird bestimmt und der Entwurf visualisiert, um das Design dann besser zu verstehen, damit es wiederverwendet werden kann. Das neue Design wird für eine effiziente zukünftige Wiederverwendung vorbereitet, optional im IP-XACT-Format.